#### Available online at www.sciencedirect.com

# **ScienceDirect**

Energy Procedia 124 (2017) 706-711

7th International Conference on Silicon Photovoltaics, SiliconPV 2017

# Thin silicon solar cells: Pathway to cost-effective and defect-tolerant cell design

André Augusto<sup>a</sup>, Erin Looney<sup>b</sup>, Carlos del Cañizo<sup>c</sup>, Stuart G. Bowden<sup>a</sup>, Tonio Buonassisi<sup>b</sup>

<sup>a</sup>Arizona State University, Tempe, AZ 85281, USA <sup>b</sup>Massachusetts Institute of Technology, Cambridge, MA 02139, USA <sup>c</sup>Instituto de Energía Solar, Universidad Politécnica de Madrid, Spain

#### Abstract

Thinner silicon wafers are a pathway to lower cost without compromising the efficiency of solar cells. In this work, we study the recombination mechanism for thin and thick silicon heterojunction solar cells, and we discuss the potential of using more defective material to manufacture high performance thin solar cells. Modelling the performance of silicon heterojunction solar cells indicates that at open-circuit voltage the recombination is dominated by Auger and surface, representing nearly 90% of the total recombination. At maximum power point, the surface is responsible for 50 to 80% of the overall recombination, and its contribution increases inversely with the wafer thickness. The experimental results show that for lower quality CZ material with 1 ms bulk lifetime,  $60 \mu$ m-thick cells perform better than 170  $\mu$ m-thick cells. The potential efficiency gain is 1% absolute. The gains in voltage of using thinner wafers are significantly higher for the lower quality CZ material, 25 mV, than for standard CZ material,  $10 \mu$ m.

© 2017 The Authors. Published by Elsevier Ltd.

Peer review by the scientific conference committee of SiliconPV 2017 under responsibility of PSE AG.

Keywords: Thin silicon; solar cells; defect; heterojunction

# 1. Introduction

The spot price of polysilicon, which peaked in 2008 (\$475/kg), has been relatively flat in the last five years (<\$20/kg) [1]. However, in a scenario of rapid growth, materials cost and CapEx will determine the growth pace [2]. Silicon is the largest single cost-component of a module and over half of total module, capex lies in feedstock production, crystallization, and wafering [3]. The wafer requirements to produce high efficiency solar cells limit the usage of n-type ingot to as much as 75%, due to non-uniform resistivity and oxygen concentration across the ingot

[4]. Thinner wafers are a pathway to lower manufacturing cost and CapEx without compromising efficiency. By combining suitable light trapping and high-quality passivation, the optimum wafer thickness is estimated to be below 110  $\mu$ m, depending on the resistivity of the wafer and dopant type [5]. For very high-resistivity (>50  $\Omega$ cm) and n-doped wafer the optimum thickness is around 100  $\mu$ m, while for lower resistivities (<5  $\Omega$ cm) the optimum thickness is around 50 $\mu$ m [6]. Thinner solar cells operate at higher voltages, as the excess carrier density increases inversely with the thickness. They are also inherently more defect-tolerant (shorter diffusion lengths required for excellent carrier collection), an opportunity to increase ingot usage, and to use more defective and lower-cost materials (e.g. UMG-Si).

Decreasing the thickness carries new challenges including fabrication yield. Microcracks induced during the sawing process and handling are the main cause of breakage [7]. Recently [8] CEA-INES, presented their results on integration of  $80~\mu m$ -thick wafers in their existing silicon heterojunction pilot line, showing efficiencies comparable to cells manufacture on standard wafers. Moreover, they claim with minor adjustments they could run  $80~\mu m$ -thick cells in their pilot line.

In this work, we present the recombination mechanism at open-circuit voltage and at maximum power point for thin silicon heterojunction solar cells, and we discuss the potential of using more defective materials to manufacture thin solar cells.

### 2. Experimental details

At the Arizona State University pilot-line, thin heterojunction solar cells are prepared on commercial grade n-type CZ wafers with 3-5  $\Omega$ cm resistivity and initial thickness of 200  $\mu$ m. The wafers are thinned and textured using alkaline wet etching, followed by wet chemical cleaning and conditioning. The heterojunction is formed using plasma enhanced chemical vapor deposition to grow intrinsic and doped hydrogenated amorphous layers (5-10 nm), forming a pi/CZ/in stack. Indium tin oxide (ITO) is sputtered on both sides of the wafer, and silver on the rear as a mirror and rear contact, Fig. 1. The samples are than annealed at 200  $^{0}$ C for 45 min.

Fig. 1. Silicon heterojunction structure used in this study.

#### 3. Results and discussion

#### 3.1. Recombination modeling

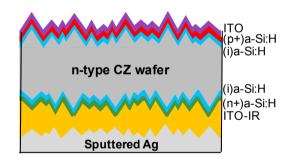

To study the recombination mechanism in our cells, the effective minority-carrier lifetime is measured using the QSSPC technique after forming the pi/CZ/in stack on wafers with different thicknesses. The effective minority-carrier lifetime is than modeled and broken down into its component parts: Auger, radiative, Shockley-Read-Hall (SRH) and front and rear surfaces lifetimes, Fig. 2. The Auger and radiative lifetimes are calculated using Richter parametrization [9], which includes the Schenk bandgap narrowing model [10] and injection dependent radiative recombination [11]. SRH recombination was calculated using a standard SRH model with symmetric recombination parameters for electrons and holes and a single trap state in the middle of the bandgap. The bulk lifetime is measured in sister samples using thick intrinsic amorphous passivation to suppress surface recombination. The surface lifetimes are fitted to the experimental data.

Fig. 2. Components of the effective minority-carrier lifetime of cells with different thicknesses and bulk qualities. The black and pink circles represent the effective minority-carrier lifetimes at MPP and  $V_{\rm OC}$  injection levels, respectively. The same pi/in stack was deposited in all samples. Details are shown in Table 1.

According to our modeling, at open-circuit voltage ( $V_{OC}$ ) the recombination is dominated by Auger and surface, representing nearly 90% of the total. At maximum power point (MPP) the surface is responsible for 50 to 80% of the recombination, the surface contribution increases inversely with the bulk thickness. Table 1 summarizes the most important results from lifetime measurements. The wafers with different bulk lifetimes but similar thicknesses show very similar performances, including implied- $V_{OC}(iV_{OC})$  and implied-fill factor (iFF).

| Thickness<br>(µm) | Bulk<br>Resistivity<br>(Ωcm) | Bulk<br>Lifetime<br>(ms) | SRV at<br>MPP (cms <sup>-1</sup> ) | iV <sub>OC</sub><br>(mV) | iFF<br>(%) |

|-------------------|------------------------------|--------------------------|------------------------------------|--------------------------|------------|

| 165               | 4                            | >6                       | 1.3                                | 735                      | 84.2       |

| 58                |                              |                          | 2.0                                | 750                      | 82.7       |

| 53                | 3                            | >4                       | 1.9                                | 752                      | 82.8       |

Table 1. Parameters calculated from the QSSPC measurements and modeling of Fig. 1.

#### 3.2. Device performance

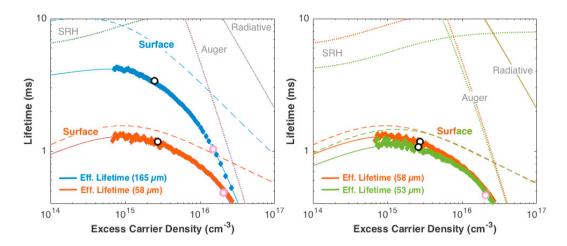

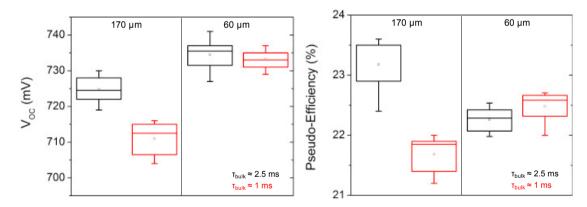

After ITO and rear silver sputtering, we measured, using Suns- $V_{OC}$  technique, the  $V_{OC}$  of samples manufactured with n-type CZ wafers with different bulk lifetimes, resistivities, and thicknesses (170  $\mu$ m and 60  $\mu$ m). The generation current is obtained from external quantum efficiency (EQE) measurements, and then the pseudo-efficiency is calculated. Lower quality CZ material shows bulk lifetimes of 1 ms at  $10^{15}$  cm<sup>-3</sup> carrier density and resistivity of 2.8  $\Omega$  cm, Fig. 3., and standard CZ material shows bulk lifetimes of 2.5 ms and resistivity of 3.5  $\Omega$  cm.

Fig. 3. Photoluminescence image of 156 mm pseudo-square n-type CZ wafers with a bulk lifetime of 1 ms. The two symmetric marks in PL image are due to wafer handling in the PECVD tool.

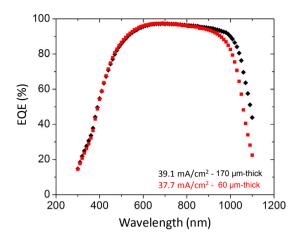

The 170  $\mu$ m-thick cells using standard CZ material show considerable higher performance than the cells manufactured with lower quality material. In the 60  $\mu$ m-thick cells the performance gap is narrowed, and cells show similar performance. The thinner cells show 10-25 mV voltage increase, Fig. 4. They also experience 1-1.5 mA cm<sup>-2</sup> current drop, due to reflection losses from the rear surface, Fig. 5. Like in Table 1., standard CZ samples used in this section show iV $_{OC}$  of 735 mV for 170  $\mu$ m-thick cells and 751 mV for 60  $\mu$ m-thick cells before ITO sputtering. The iV $_{OC}$  for lower quality CZ samples is 723 mV for 170  $\mu$ m-thick cells and 745 mV for 60  $\mu$ m-thick cells before ITO sputtering. The samples show 10-15 mV degradation in V $_{OC}$  after ITO sputtering, even after annealing treatment [12].

Fig. 4. Open-circuit voltages and pseudo-efficiencies of 170  $\mu$ m and 60  $\mu$ m-thick silicon heterojunction solar cells manufactured on 1 ms and 2.5 ms bulk lifetime CZ n-type materials. 60 samples were measured in this study. The pseudo-FF for standard CZ are 81.8% and 81.3 for the 170  $\mu$ m and 60  $\mu$ m thick cells, respectively. For lower quality CZ the values are 79.9% and 81.2%. The currents to calculate the pseudo-efficiency were obtained from the EQE measurements in Fig. 5.

Fig. 5. Representative external quantum efficiency of  $170 \mu m$  and  $60 \mu m$ -thick silicon heterojunction solar cells. The generation current is 1-1.5 mA cm<sup>-2</sup> lower for thin cells due to IR reflection from the rear surface. There is no significant difference between standard and lower quality CZ

Preliminary simulation results indicate a practical path to reach 24% efficiencies for thin cells with lower quality n-type CZ. Optimization of the ITO sputtering is necessary to mitigate damage in  $V_{\rm OC}$  and to reduce parasitic light absorption in the blue region. To increase further the current, we need to apply more advanced light-trapping schemes to improve the performance in the infrared [13].

#### 4. Conclusions

We experimentally demonstrate that thin silicon heterojunction cells enable the use of more defective material to manufacture high-performance devices. With standard CZ material, thick cells perform better than thin cells, due to current losses in the infrared. For lower quality CZ material, thin cells perform better than thick cells, despite the lower generation current of thin cells. The gains in voltage of using thinner wafers are significantly higher for the lower quality CZ material ( $\Delta V$ =25 mV) than for standard CZ material ( $\Delta V$ =10 mV). Further improvements to prevent sputtering damaging and more advanced light trapping to increase generation current are required to unveil the full potential of thinner cells.

## Acknowledgements

This work was supported by QESST, jointly funded by the NSF and DOE and by PVRD funded through the DOE CA No. EEC-1041895. E. Looney gratefully acknowledges funding from NSF Graduate Research Fellowship program. C. del Cañizo acknowledge the funding from the Spanish Ministerio de Economía y Competitividad through TABACO project (ENE2014-56069-C4-2-R) and the Comunidad de Madrid through the MADRID-PV one (S2013/MAE-2780). A. Augusto acknowledges DOD funding under DODRIF13-OEPP01-P-0020.

#### References

- [1] https://www.washingtonpost.com/business/economy/prices-flat-in-polysilicon-market/2013/07/23/914479d0-f3e4-11e2-9434-60440856fadf\_graphic.html

- [2] D. M. Powell, M. T. Winkler, A. Goodrich, and T. Buonassisi, "Modeling the cost and minimum sustainable price of crystalline silicon photovoltaic manufacturing in the United States", IEEE J. Photovoltaics 3(2), 662–668 (2013).

- [3] D. M. Powell, R. Fu, K. Horowitz, P. A. Basore, M. Woodhouse, T. Buonassisi, "The capital intensity of photovoltaics manufacturing: barrier to scale and opportunity for innovation", Energy Environ. Sci. 8(12), 3395-3408 (2015).

- [4] Han Xu, "Characterization of n-type Mono-crystalline Silicon Ingots Produced by Continuous Czochralski (Cz) Technology", Energy Procedia 77, 658 – 664 (2015).

- [5] M. J. Kerry, A. Cuevas, and P. Campbell, "Limiting efficiency of crystalline silicon solar cells due to Coulomb-enhanced Auger recombination", Prog. Phot. Res. Appl. 11(2), 97–104 (2003)

- [6] A. Richter, Martin Hermle, and Stefan W. Glunz, "Reassessment of the limiting efficiency for crystalline silicon solar cells", IEEE J. of Photovoltaics 3(4), 1184-1191 (2013)

- [7] E. Careceda et al. "Crack origin and detection in thin crystaline solar cells in a production line", Proceeding of EU PVSEC, Milan, Italy, 2007, pp. 1168-70.

- [8] S. Harrison, et al., "How to deal with thin wafers in aheterojunction solar cells industrial pilot line: first analyses of the integration of cells to 70μm thick in production mode", Proceeding of 32th EU PVSEC, Germany, 2016, pp. 358-62.

- [9] A. Richter, S. W. Glunz, F. Werner, J. Schmidt, A. Cuevas, "Improved quantitative description of Auger recombination in crystalline silicon", Phys. Rev. 86(16), 165202 (2012)

- [10] A. Schenk," Finite-temperature full random-phase approximation model of band gap narrowing for silicon device simulation", J. Appl. Phys. 84(7), 3684-3685 (1998)

- [11] PP. Altermatt, F. Geelhaar, T. Trupke, X. Dai, A. Neisser, and E. Daub," Injection dependence of spontaneous radiative recombination in crystalline silicon: Experimental verification and theoretical analysis", Appl. Phys. Lett. 88(26): 261901 (2006)

- [12] D. Zhang, A. Tavakoliyaraki, Y. Wu, RACMM Van Swaaij, and M. Zeman, 'Influence of ITO deposition and post annealing on HIT solar cell structures", Energy Procedia 8, 207-213 (2011)

- [13] P. Spinelli and A. Polman, "Light trapping in thin Crystalline Si solar cells using surface Mie scatterers", IEEE J. of Photovoltaics 4(2), 554-559 (2014)